Paper 53 Entered: March 1, 2022

# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD INTEL CORPORATION and XILINX, INC., Petitioner, v. FG SRC LLC, Patent Owner. IPR2020-01449

Patent 7,149,867 B2

Before KALYAN K. DESHPANDE, GREGG I. ANDERSON, and KARA L. SZPONDOWSKI, *Administrative Patent Judges*.

${\bf SZPONDOWSKI}, Administrative\ Patent\ Judge.$

JUDGMENT

Final Written Decision

Determining All Challenged Claims Unpatentable

Denying Patent Owner's Motion to Amend

35 U.S.C. § 318(a)

<sup>&</sup>lt;sup>1</sup> Xilinx, Inc. filed a motion for joinder and a petition in IPR2021-00633, which were granted, and, therefore, Xilinx, Inc. has been joined as petitioner in this proceeding.

## I. INTRODUCTION

We instituted an *inter partes* review of claims 1–19 of U.S. Patent 7,149,867 B2 (Ex. 1001, "the '867 patent"), in response to a Petition (Paper 1, "Pet") filed by Intel Corporation ("Petitioner"). Paper 13 ("Dec."). During the trial, FG SRC LLC ("Patent Owner") filed a Response (Paper 34, "PO Resp."), Petitioner filed a Reply (Paper 40, "Reply"), and Patent Owner filed a Sur-reply (Paper 44, "Sur-reply").

Patent Owner also filed a Motion to Amend the claims of the '867 patent. Paper 26. After considering Petitioner's Opposition to the Motion to Amend (Paper 36), we issued Preliminary Guidance on Patent Owner's Motion (Paper 38). Patent Owner subsequently filed a Revised Motion to Amend the claims of the '867 patent that includes proposed substitute claims 20–38. Paper 41 ("Mot. Amend"). Petitioner opposed Patent Owner's Revised Motion to Amend (Paper 45, "Opp. Amend"), Patent Owner replied (Paper 49, "Reply Amend"), and Petitioner filed a Sur-reply (Paper 50, "Surreply Amend").

An oral hearing was held on January 6, 2022, and a copy of the transcript was entered into the record. Paper 52 ("Tr.).

We have jurisdiction under 35 U.S.C. § 6. This Decision is a Final Written Decision under 35 U.S.C. § 318(a) as to the patentability of the claims on which we instituted trial. Based on the complete record, Petitioner has shown, by a preponderance of the evidence, that claims 1–19 of the '867 patent are unpatentable. We also deny Patent Owner's Revised Motion to Amend, because Patent Owner has not met its burden in asserting that proposed substitute claims 20–38 have written description support in the original application that issued as the '867 patent.

### II. BACKGROUND

### A. Real Parties in Interest

Petitioner identifies Intel Corporation as the sole real party in interest. Pet. 2. Patent Owner identifies FG SRC LLC as the sole real party in interest. Paper 4, 2.

## B. Related Matters

The parties advise that the '867 patent is the subject of the following district court litigations:

FG SRC LLC v. Intel Corporation, 6:20-cv-00315-ADA (W.D. Tex.), filed April 24, 2020 ("the co-pending district court litigation");

*FG SRC LLC v. Xilinx, Inc.*, 1:20-cv-00601-LPS (D. Del.), filed April 30, 2020; and

SRC Labs, LLC et al. v. Amazon Web Services, Inc., et al., 2:18-cv-00317-JLR (W.D. Wash.), filed February 26, 2018.

Pet. 2; Paper 4, 2. Petitioner also advises that the '867 patent was the subject of IPR2019-00103 (institution denied on May 10, 2019). Pet. 2.

# C. The '867 Patent (Ex. 1001)

The '867 patent issued from Application No. 10/869,200 filed June 16, 2004, and claims the benefit of Provisional Application No. 60/479,339, filed June 18, 2003. Ex. 1001, codes (21), (22), (60). The '867 patent is titled "System and Method of Enhancing Efficiency and Utilization of Memory Bandwidth in Reconfigurable Hardware" and is generally directed to "enhancing the efficiency and utilization of memory bandwidth in reconfigurable hardware" and "implementing explicit memory hierarchies in reconfigurable processors that make efficient use of off-board, on-board, on-chip storage and available algorithm locality." *Id.* at code (57), 1:15–24.

According to the '867 patent, there was a growing need to develop improved memory hierarchies that limited overhead of a memory hierarchy without also reducing bandwidth efficiency and utilization. Ex. 1001, 3:57–60. The '867 patent describes a system including a memory hierarchy and a reconfigurable processor that includes a data prefetch unit. *Id.* at 4:4–10, 5:60–62, 6:9–13, 7:34–48. The '867 patent states that a "Reconfigurable Processor" is "a computing device that contains reconfigurable components such as FPGAs [(field programmable gate arrays)] and can, through reconfiguration, instantiate an algorithm as hardware." *Id.* at 5:26–29. The '867 patent states that a "Data prefetch Unit" is "a functional unit [a set of logic that performs a specific operation] that moves data between members of a memory hierarchy [a collection of memories]," where such "movement may be as simple as a copy, or as complex as an indirect indexed strided copy into a unit stride memory." *Id.* at 5:34–43.

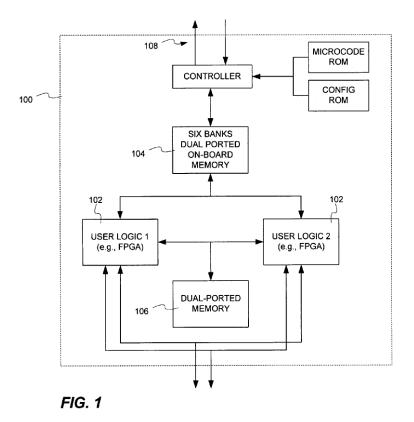

Figure 1 of the '867 patent, reproduced below, shows a reconfigurable processor (RP) 100 of the claimed invention. *Id.* at 4:38–40.

Figure 1 depicts a reconfigurable processor (RP) 100. *Id.* at 4:38–40.

Figure 1 depicts reconfigurable processor 100, which "may be implemented using field programmable gate arrays (FPGAs) or other reconfigurable logic devices, that can be configured and reconfigured to contain functional units and interconnecting circuits, and a memory hierarchy comprising on-board memory banks 104, on-chip block RAM 106, registers wires, and a connection 108 to external memory." *Id.* at 6:5–11. In addition, "[o]n-chip reconfigurable components 102 create memory structures such as registers, FIFOs, wires and arrays using block RAM." *Id.* at 6:11–14. "Dual-ported memory 106 is shared between on-chip reconfigurable components 102." *Id.* at 6:14–15. "The reconfigurable processor 100 also implements user-defined computational logic . . . constructed by programming an FPGA to implement a particular interconnection of computational functional units." *Id.* at 6:15–19. "In a

particular implementation, a number of RPs 100 are implemented within a memory subsystem of a conventional computer, such as on devices that are physically installed in dual inline memory module (DIMM) sockets of a computer." *Id.* at 6:19–23. "In this manner the RPs 100 can be accessed by memory operations and so coexist well with a more conventional hardware platform." *Id.* at 6:23–25. The '867 patent explains that "[u]nlike conventional static hardware platforms... the memory hierarchy provided in a RP 100 is reconfigurable" and "through the use of data access units and associated memory hierarchy components, computational demands and memory bandwidth can be matched." *Id.* at 7:17–22.

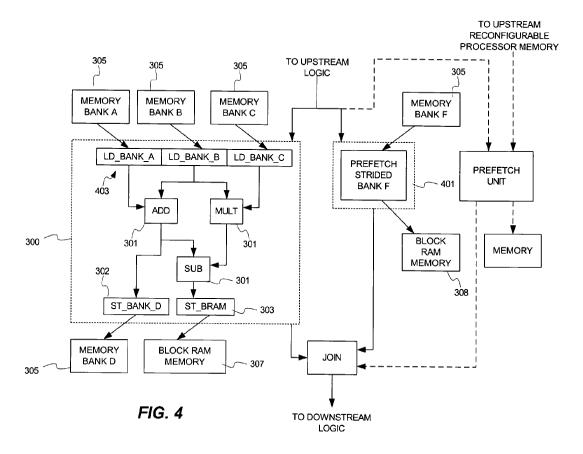

One or more data prefetch units are used to improve the memory hierarchy and bandwidth efficiency and utilization. *Id.* at 3:58–60, 8:62–65. Fig. 4 of the '867 patent, reproduced below, depicts a logic block 300 with an addition of a data prefetch unit 401. *Id.* at 4:44–46.

Figure 4 illustrates a logic block 300 (a block composed of computational functional units capable of taking data and producing results with each clock pulse) with the addition of a data prefetch unit 401. *Id.* at 7:6–8, 7:34–35.

Logic block 300 includes computational functional units (computational logic) 301, 302, and 303, a control, and data access functional units 403 that present data to computational logic 301, 302, and 303. *Id.* at 7:25–48, Fig. 4. Data prefetch unit 401 moves data from one member of the memory hierarchy 305 to another 308 (a block RAM memory). *Id.* at 7:34–37, Fig. 4. Data prefetch unit 401 operates "independently of other functional units 301, 302, and 303 and can therefore operate prior to, in parallel with, or after computational logic." *Id.* at 7:37–40. In addition, data prefetch unit 401 may be "operated independently of logic block 300 that uses prefetched data." *Id.* at 7:45–48. Data prefetch

IPR2020-01449 Patent 7,149,867 B2

unit 401 deposits data into the memory hierarchy, where computational logic 301, 302, and 303 can access it through data access units. *Id.* at 7:42–44.

The '867 patent explains:

An important feature of the present invention is that many types of data prefetch units can be defined so that the prefetch hardware can be configured to conform to the needs of the algorithms currently implemented by the computational logic. The specific characteristics of the prefetch can be matched with the needs of the computational logic and the format and location of data in the memory hierarchy.

*Id.* at 7:49–55. The '867 patent provides examples of configuring a data prefetch unit depending on the needs of the computational logic. *Id.* at 7:52–62, 8:3–21, Figs. 9A–9B.

### D. Illustrative Claims

Among the challenged claims, claims 1, 9, and 13 are independent. Independent claims 1, 9, and 13 are reproduced below, with brackets noting Petitioner's identifiers.

- 1. [preamble] A reconfigurable processor that instantiates an algorithm as hardware comprising:

- [1(a)] a first memory having a first characteristic memory bandwidth and/or memory utilization; and

- [1(b)] a data prefetch unit coupled to the first memory, [1(c)] wherein the data prefetch unit retrieves only computational data required by the algorithm from a second memory of second characteristic memory bandwidth and/or memory utilization and places the retrieved computational data in the first memory [1(d)] wherein the data prefetch unit operates independent of and in parallel with logic blocks using the computional [sic] data, and [1(e)] wherein at least the first memory and data prefetch unit are configured to conform to needs of the algorithm, and [1(f)] the data prefetch unit is configured to match format and location of data in the second memory.

9. [preamble] A reconfigurable hardware system, comprising:

[9(a)] a common memory; and

[9(b)] one or more reconfigurable processors that can instantiate an algorithm as hardware coupled to the common memory, [9(c)] wherein at least one of the reconfigurable processors includes a data prefetch unit to read and write only data required for computations by the algorithm between the data prefetch unit and the common memory [9(d)] wherein the data prefetch unit operates independent of and in parallel with logic blocks using the computational data, and [9(e)] wherein the data prefetch unit is configured to conform to needs of the algorithm and [9(f)] match format and location of data in the common memory.

# 13. [preamble] A method of transferring data comprising:

[13(a)] transferring data between a memory and a data prefetch unit in a reconfigurable processor; and

[13(b)] transferring the data between a computational unit and a data access unit, [13(c)] wherein the computational unit and the data access unit, and the data prefetch unit are configured to conform to needs of an algorithm implemented on the computational unit and transfer only data necessary for computations by the computational unit, and [13(d)] wherein the prefetch unit operates independent of and in parallel with the computational unit.

Ex. 1001, 12:39-54; 13:13-26; 14:1-11.

### E. Evidence

Petitioner relies on the following references (see Pet. 4–5).

| Reference | Exhibit | Patent/Printed Publication                                                                                                                                                                                                           |

|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Zhang     | 1003    | Xingbin Zhang et al., Architectural Adaptation of Application-Specific Locality Optimizations, published in the Proceedings of the International Conference on Computer Design - VLSI in Computers and Processors (IEEE, October 12– |

|       |      | 15, 1997), 150–156                            |

|-------|------|-----------------------------------------------|

| Gupta | 1004 | Rajesh Gupta, Architectural Adaptation in     |

|       |      | AMRM Machines, Proceedings of the IEEE        |

|       |      | Computer Society Workshop on VLSI 2000        |

|       |      | (IEEE, April 27–28, 2000), 75–79              |

| Chien | 1005 | Andrew A. Chien et al., MORPH: A System       |

|       |      | Architecture for Robust High Performance      |

|       |      | Using Customization (An NSF 100 TeraOps       |

|       |      | Point Design Study), Proceedings of Frontiers |

|       |      | '96 – The Sixth Symposium on the Frontiers of |

|       |      | Massively Parallel Computing (IEEE, October   |

|       |      | 27–31, 1996), 336–345                         |

In addition, Petitioner relies on the Declarations of Rajesh K. Gupta, Ph.D. (Exs. 1010, 1030), Declarations of Jacob Robert Munford (Exs. 1012, 1031), Declaration of Gordon MacPherson (Ex. 1027), Declaration of Eileen D. McCarrier (Ex. 1028), Declaration of Austin Schnell (Ex. 1029), and Declaration of Dr. Stanley Shanfield (Ex. 1006).

Patent Owner relies on the Declaration of Dr. William Mangione-Smith (Ex. 2028) and Declaration of Ryan Kastner, Ph.D. (Ex. 2010).

Deposition transcripts have been entered into the record for Dr. Gupta (Ex. 1039), Mr. MacPherson (Ex. 1040), Dr. Shanfield (Exs. 1043, 2029), and Dr. Mangione-Smith (Ex. 1044).

### F. Prior Art and Asserted Grounds

Petitioner asserts that claims 1–19 are unpatentable on the following grounds (Pet. 5):

| Claims Challenged | 35 U.S.C.<br>§ <sup>2</sup> | References          |

|-------------------|-----------------------------|---------------------|

| 1, 2, 4–8, 13–19  | 103                         | Zhang, Gupta        |

| 3, 9–12           | 103                         | Zhang, Gupta, Chien |

### III. ANALYSIS

# A. Legal Standards

A claim is unpatentable under 35 U.S.C. § 103(a) if "the differences between the subject matter sought to be patented and the prior art are such that the subject matter as a whole would have been obvious at the time the invention was made to a person having ordinary skill in the art to which said subject matter pertains." *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 406 (2007). The question of obviousness is resolved on the basis of underlying factual determinations, including: (1) the scope and content of the prior art; (2) any differences between the claimed subject matter and the prior art; (3) the level of skill in the art; and (4) objective evidence of nonobviousness, i.e., secondary considerations. *See Graham v. John Deere Co.*, 383 U.S. 1, 17–18 (1966).

A patent claim "is not proved obvious merely by demonstrating that each of its elements was, independently, known in the prior art." KSR, 550

<sup>&</sup>lt;sup>2</sup> The Leahy-Smith America Invents Act ("AIA"), Pub. L. No. 112-29, 125 Stat. 284 (2011), amended 35 U.S.C. § 103, effective March 16, 2013. Because the application from which the '867 patent issued was filed before this date, the pre-AIA version of § 103 applies.

U.S. at 418. An obviousness determination requires finding "both 'that a skilled artisan would have been motivated to combine the teachings of the prior art references to achieve the claimed invention, and that the skilled artisan would have had a reasonable expectation of success in doing so." *Intelligent Bio-Sys., Inc. v. Illumina Cambridge Ltd.*, 821 F.3d 1359, 1367–68 (Fed. Cir. 2016) (citation omitted); *see KSR*, 550 U.S. at 418. Further, an assertion of obviousness "cannot be sustained by mere conclusory statements; instead, there must be some articulated reasoning with some rational underpinning to support the legal conclusion of obviousness." *KSR*, 550 U.S. at 418; *In re NuVasive, Inc.*, 842 F.3d 1376, 1383 (Fed. Cir. 2016) (a finding of a motivation to combine "must be supported by a 'reasoned explanation'" (citation omitted)).

# B. Level of Ordinary Skill in the Art

Petitioner asserts a person of ordinary skill in the art "would have had an undergraduate degree in electrical engineering or related field with at least three years of experience in computer processor architecture and FPGAs, a master's degree with two or more years of experience in those fields, or an equivalent combination of education and experience." Pet. 14 (citing Ex.  $1006 \, \P \, 67$ ).

Patent Owner does not dispute Petitioner's proposed level of skill. See generally PO Resp.

We find Petitioner's proposal is consistent with the level of ordinary skill in the art reflected by the prior art of record, and, therefore, adopt Petitioner's proposed level of ordinary skill in the art for purposes of this Decision. *See Okajima v. Bourdeau*, 261 F.3d 1350, 1355 (Fed. Cir. 2001).

# C. Claim Construction

We construe each claim "in accordance with the ordinary and customary meaning of such claim as understood by one of ordinary skill in the art and the prosecution history pertaining to the patent," the same standard used to construe the claim in a civil action. 37 C.F.R. § 42.100(b) (2020).

# 1. Agreed Constructions

The parties agree to the construction of the following terms:

| Claim term                   | Proposed Construction                                  |

|------------------------------|--------------------------------------------------------|

| Reconfigurable               | a computing device that contains reconfigurable        |

| Processor                    | components such as FPGAs and can, through              |

|                              | reconfiguration, instantiate an algorithm as hardware  |

| Data Prefetch Unit           | a functional unit that moves data between members of   |

|                              | a memory hierarchy. The movement may be as             |

|                              | simple as a copy, or as complex as an indirect         |

|                              | indexed strided copy into a unit stride memory         |

| Data Access Unit             | a functional unit that accesses a component of a       |

|                              | memory hierarchy, and delivers data directly to the    |

|                              | computational logic                                    |

| Functional Unit <sup>3</sup> | a set of logic that performs a specific operation. The |

|                              | operation may for example be arithmetic, logical,      |

|                              | control, or data movement. Functional units are used   |

|                              | as building blocks of reconfigurable logic             |

| Memory                       | a collection of memories                               |

| Hierarchy <sup>4</sup>       |                                                        |

\_

<sup>&</sup>lt;sup>3</sup> Petitioner states that although not directly recited in the claims, this term is used in the '867 patent's definition of "data prefetch unit" and "data access unit." Pet. 15; Ex. 1001, 5:40–46.

<sup>&</sup>lt;sup>4</sup> Petitioner states although not directly recited in the claims, this term is used in the '867 patent's definition of "data prefetch unit" and "data access unit." Pet. 15; Ex. 1001, 5:40–46.

IPR2020-01449 Patent 7,149,867 B2

Pet. 14–16 (citing Ex. 1001; Ex. 1006); PO Resp. 29–30. We adopt these agreed constructions for purposes of this Decision.

Patent Owner also states that in the co-pending district court litigation, the parties have agreed to the following constructions:

| Claim term               | Agreed Construction                            |

|--------------------------|------------------------------------------------|

| (Preamble) A             | Preamble is limiting                           |

| reconfigurable processor |                                                |

| that instantiates an     |                                                |

| algorithm as hardware    |                                                |

| Common Memory            | an external memory shared by processors in     |

|                          | a multiprocessor system                        |

| Computational Unit       | a functional unit of a reconfigurable          |

|                          | processor that performs a computation          |

| the Data Prefetch Unit   | the data prefetch unit receives the results of |

| Receives Processed Data  | the algorithm                                  |

| Configured To Conform to | configured in reconfigurable logic to          |

| Needs of The Algorithm   | conform to the needs of the algorithm          |

| Reconfigurable Logic     | reconfigurable logic is composed of an         |

|                          | interconnection of functional units, control,  |

|                          | and storage that implements an algorithm       |

|                          | and can be loaded into a Reconfigurable        |

|                          | Processor                                      |

PO Resp. 30. We further adopt these agreed constructions for purposes of this Decision.

# 2. Patent Owner's Proposed Constructions

Patent Owner proposes construction for two terms.

a) "retrieves only computational data required by the algorithm from a second memory . . . and places the retrieved computational data in the first memory" (limitation l(c))

Patent Owner argues that this limitation should be construed as "retrieves from a second memory that computational data which is required by the algorithm *and no other computational data* ... and places the

IPR2020-01449 Patent 7,149,867 B2

retrieved computational data in the first memory." POResp. 31–32 (emphasis added).

Patent Owner contends that "[t]he plain meaning requires that no superfluous computational data is transferred to the first memory." *Id.* at 31. In support of its proposed construction, Patent Owner identifies column 9, lines 1–5 of the '867 patent, which states "an important feature of the present invention is the ability to implement various kinds or styles of prefetch units to meet the needs of a particular algorithm being implemented by computational elements." *Id.* Patent Owner also relies on column 9, lines 8–10, which states "in most cases the function being implemented by components 301 would change and therefore alter the decision as to which prefetch strategy is most appropriate." *Id.* at 31–32. Patent Owner also relies on column 9, lines 35–40, which states "[g]ains are made by delivering only requested data from transfer buffer 1305 (not the remainder of a data block as in cache line oriented systems) by eliminating the need to transfer an index array either to the processor or to the memory controller." *Id.* at 32.

Petitioner contends that Patent Owner does not rely on this construction to overcome the prior art, and Patent Owner's expert does not rely on (or even recite) this construction. Reply 2 (citing PO Resp. 40–44; Ex. 1044, 28:18–29:5, 32:10–14, 107:19–108:7). Petitioner also argues that Patent Owner's proposed construction is unsupported by intrinsic evidence. *Id.* at 3–4.

Patent Owner has not explained the impact of this proposed claim construction on its arguments supporting patentability of the claims. We disagree with Patent Owner that its proposed construction is the "plain and ordinary meaning," because the claim language recites "retrieves *only*

computational data *required by the algorithm* from a second memory," and does not require the additional limitation "and no other computational data." Under these circumstances, we decline to rewrite the claim language to include additional words that are not present in the claim, e.g., "and no other computational data." *See Hoganas AB v. Dresser Indus., Inc.*, 9 F.3d 948, 950 (Fed. Cir. 1993) (quoting *E.I. Du Pont de Nemours & Co. v. Phillips Petroleum Co.*, 849 F.2d 1430, 1433 (Fed. Cir. 1988)) ("It is improper for a court to add 'extraneous' limitations to a claim, that is, limitations added 'wholly apart from any need to interpret what the patentee meant by particular words or phrases in the claim."").

Moreover, in light of the parties' arguments, we determine that we need not expressly construe this term. *See Nidec Motor Corp. v. Zhongshan Broad Ocean Motor Co.*, 868 F.3d 1013, 1017 (Fed. Cir. 2017) ("[W]e need only construe terms 'that are in controversy, and only to the extent necessary to resolve the controversy." (quoting *Vivid Techs., Inc. v. Am. Sci. & Eng'g, Inc.*, 200 F.3d 795, 803 (Fed. Cir. 1999))). We agree with Petitioner that Patent Owner does not rely on this construction to overcome the prior art; for example, Dr. Mangione-Smith testified that he had not been given or applied any particular claim construction. *See* Ex. 1044, 28:18–32:14; 107:19–109:4; *see* PO Resp. 40–44; Ex. 2028 ¶ 74.

b) "read and write only data required for computations by the algorithm between the data prefetch unit and the common memory" (claim 9)

Patent Owner proposes that this term should be construed as "read, using the data prefetch unit, only data required for computations by the algorithm from common memory and write, using the data prefetch unit, only data required for computations by the algorithm." PO Resp. 33. In

support of its construction, Patent Owner states that "[t]his term should be accorded its plain and ordinary meaning." *Id*.

Petitioner contends that Patent Owner does not rely on this construction to overcome the prior art, and Patent Owner's expert does not rely on (or even recite) this construction. Reply 2 (citing PO Resp. 40–44; Ex. 1044, 28:18–29:5, 32:10–14, 107:19–108:7). Petitioner also argues that Patent Owner's proposed construction is unsupported by intrinsic evidence. *Id.* at 3–4.

Patent Owner has not explained the impact of this proposed claim construction on its arguments supporting patentability of the claims. Moreover, Patent Owner does not explain why we should adopt this proposed construction, or provide any supporting intrinsic evidence. Moreover, given that Patent Owner relies on the same arguments for claim 9 as it presented for claim 1 (which does not recite this limitation), we agree with Petitioner that Patent Owner does not rely on this construction in order to overcome the prior art. *See* PO Resp. 53–55; *see*, *e.g.*, Ex. 1044, 28:18–32:14 (Dr. Mangione-Smith testifying that he had not been given or applied any particular claim construction). Accordingly, we determine that we need not expressly construe this term to resolve the parties' dispute.

- D. The Asserted Prior Art References

- 1. Zhang (Ex. 1003)

Zhang is a paper published by the Institute of Electrical and Electronics Engineers, Inc. (hereafter "IEEE") as part of the *Proceedings of the International Conference on Computer Design-VLSI in Computers and Processors*. Ex. 1003, 1–2, 4.5 Zhang describes "a machine architecture

<sup>&</sup>lt;sup>5</sup> Citations to Exhibit 1003 are to the page numbering provided by Petitioner.

that integrates programmable logic into key components of the system with the goal of customizing architectural mechanisms and policies to match an application," using application-specific hardware assists. *Id.* at 12 (Abstract). Zhang "demonstrate[s] that application-specific hardware assists and policies can provide substantial improvements in performance on a per application basis." *Id.* Zhang's architecture "integrates small blocks of programmable logic into key elements of a baseline architecture, including processing elements, components of the memory hierarchy, and the scalable interconnect, to provide *architectural adaptation*—the customization of architectural mechanisms and policies to match an application." *Id.* at 13. Zhang explains that architectural adaptation provides mechanisms for application-specific hardware assists to overcome rigid architectural choices that do not work well across different applications, as "integration of programmable logic with memory components enables application-specific locality optimizations." *Id.* at 13–14.

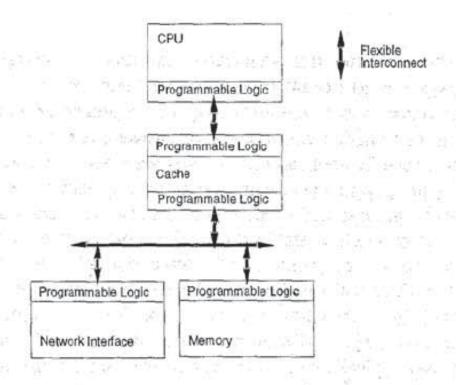

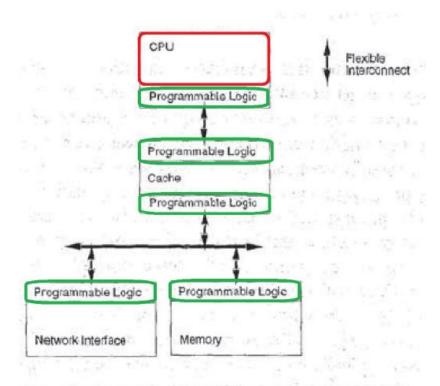

Zhang's architecture is depicted in Figure 2 below:

Figure 2. An Architecture for Adaptation

Figure 2 of Zhang depicts programmable logic integrated with CPU, cache, network interface, and memory.

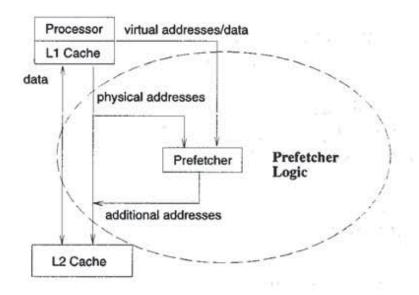

Zhang presents "two case studies of architectural adaption using application-specific knowledge to enhance latency tolerance and efficiently utilize network bisection on multiprocessors." Ex. 1003, 14. The first case study uses architectural adaptation for prefetching and exploits application access pattern information. *Id.* at 15. Figure 4 of Zhang, reproduced below, depicts a prefetcher implementation for Zhang's first case study, using programmable logic integrated with the L1 cache. *Id.*

Figure 4. Organizations of Prefetcher Logic

Figure 4 shows a prefetcher implementation using programmable logic integrated with the L1 cache.

The prefetcher in Figure 4 requires two pieces of application-specific information: address ranges and memory layout of the target data structures. *Id.* at 15. The address range, which is application dependent, is needed to indicate memory bounds where prefetching is likely to be useful. *Id.*Prefetching can be enabled or disabled, and is triggered only by read misses. *Id.* Once the prefetcher is enabled, it determines what and when to prefetch by checking virtual addresses of cache lookups to check whether a matrix element is being accessed. *Id.* In one example, records spanning multiple cache lines are targeted to "prefetch[] all fields of a matrix element structure whenever some field of the element is accessed." *Id.* Because each matrix element (which is padded to 64 bytes) spans two cache lines (in a cache with cache line size of 32 bytes), the prefetcher generates an additional L2 cache lookup address from the given physical address that prefetches the other cache line not yet referenced. *Id.* In a second example, particular pointer

fields (those likely to be traversed when their parent structures are accessed) are targeted. *Id.* at 15–16. For example, in a sparse matrix-vector multiply, the record pointed to by the *nextRow* field is accessed close in time with the current matrix element. *Id.* A prefetcher generates an additional address after the initial cache miss is satisfied using the *nextRow* pointer value embedded in the data returned by the L2 cache. *Id.* at 16.

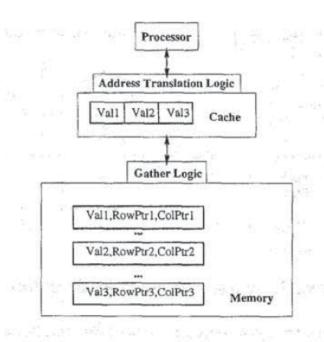

Zhang's second case study uses a sparse matrix-matrix multiply routine to show architectural adaptation that improves data reuse and reduces data traffic between the memory unit and the processor. *Id.* at 15–16. "The architectural customization aims to send only used fields of matrix elements during a given computation to reduce bandwidth requirement using dynamic scatter and gather." *Id.* at 16. "The two main ideas are prefetching of whole rows or columns using pointer chasing in the memory module and packing/gathering of only the used fields of the matrix element structure." *Id.* Figure 5 of Zhang, reproduced below, illustrates an architecture including a cache and a main memory module, and containing two units of logic, an address translation logic and a gather logic.

Figure 5. Scatter and Gather Logic

Figure 5 shows a scatter and gather logic using two units of logic, an address translation logic and a gather logic. *Id.* at 16.

# 2. Gupta (Ex. 1004)

Gupta is a paper published by IEEE as part of the *Proceedings of the IEEE Computer Society Workshop on VLSI 2000*. Ex. 1004, 1, 3, 6.6 Gupta describes an Adaptive Memory Reconfiguration Management (AMRM) prototype architecture that implements a board-level prototype designed to "simulate a range of memory hierarchies for applications running on a host processor" and "supports configurability of [a] cache memory via an onboard FPGA-based memory controller." *Id.* at 8–10. The goals of Gupta's AMRM prototype are that "it be adaptable to many different memory hierarchy architectures," "be useful for running real time program execution or even memory simulations," and demonstrate "a specific mechanism for

<sup>&</sup>lt;sup>6</sup> Citations to Exhibit 1004 are to the page numbering provided by Petitioner.

IPR2020-01449 Patent 7,149,867 B2

latency management... to provide significant performance boost for the class of applications characterized by frequent accesses to linked data structures scattered in the physical memory." *Id.* at 9–10.

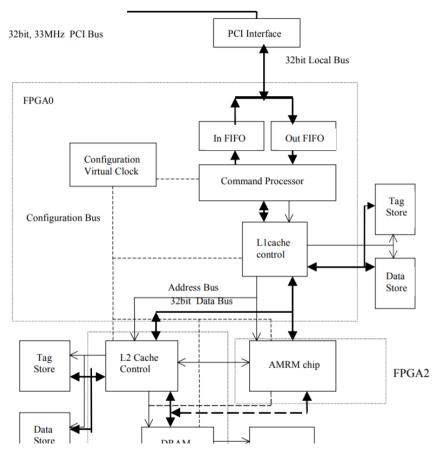

Figure 1 of Gupta, reproduced below, illustrates an AMRM prototype board.

Figure 1: AMRM Phase I Prototype Board

Figure 1 illustrates the main components of an AMRM prototype board.

As shown in Figure 1, an AMRM prototype board includes a general 3-level memory hierarchy plus support for an AMRM ASIC chip implementing architectural assists within a CPU-L1 datapath. *Id.* at 10. The FPGAs on the board contain controllers for the SRAM, DRAM and L1 cache. *Id.* The AMRM chip is positioned between the L1 cache and the rest

of the system and can be accessed in parallel with the L2 cache. *Id.* at 11. The AMRM chip can thus accept and supply data coming from or going to the L1 cache. *Id.* The AMRM chip may contain a write buffer or a prefetch unit to access L2, and also has access to the memory interface and can prefetch from memory. *Id.*

# 3. *Chien (Ex. 1005)*

Chien is a paper published by the IEEE Computer Society Press as part of the *Proceedings of Frontiers '96–The Sixth Symposium on the Frontiers of Massively Parallel Computing.* Ex. 1005, 1–2, 5.7 Chien describes a design and architecture of a MultiprocessOr with Reconfigurable Parallel Hardware (MORPH) that "uses reconfigurable logic blocks integrated with the system core to control policies, interactions, and interconnections" and has "configurability [that] supports component software and interoperabilty frameworks, allowing direct support for application-specified patterns, objects, and structures." *Id.* at 7 (emphasis omitted). Chien explains that "[t]he benefit of configurable logic is that it can be used to customize the machine's behavior to better match that required by the application—in essence a machine can be tuned for each application with little or no performance penalty for this generality." *Id.*

### Chien states:

The key elements of the MORPH architecture include processing elements and memory elements embedded in a scalable interconnect. The scalable interconnect flexibly connects all parts of the system with fast packet routing, efficiently exploiting the wiring resources provided by the system packaging []. The hardware structure allows adaptation of data transport, coordination, association (for granularity), and efficient computation. . . MORPH could be used to implement either a

<sup>&</sup>lt;sup>7</sup> Citations to Exhibit 1005 are to the page numbering provided by Petitioner.

cache-coherent machine, a non-cache coherent machine, or even clusters of cache coherent machines connected by put/get or message passing. Varying the mix of processing and memory elements supports a wide range of machine configurations and balances. Examples of other possible changes include changes in cache block size, branch predictors, or prefetch policies.

*Id.* at 10.

4. Printed Publication Status of Zhang, Gupta, and Chien

a) Background

In the Institution Decision, we determined that Petitioner had established a reasonable likelihood that it would prevail in showing the unpatentability of the challenged claims over the asserted prior art. Dec. 34–44. This included a determination that, for purposes of institution and in accordance with the Board's precedential decision in *Hulu, LLC v. Sound View Innovations, LLC*, IPR2018-01039, Paper 29 at 13 (PTAB Dec. 20, 2019) (precedential), Petitioner had established a reasonable likelihood that Zhang, Gupta, and Chien each qualify as prior art printed publications. Dec. 19–23. We stated that "[t]o the extent Patent Owner continues to challenge the printed publication status of these references after institution, the parties are requested to further develop the record on this issue." *Id.* at 44. Following the Institution Decision, we granted Petitioner's Motion to Submit Supplemental Information pursuant to 37 C.F.R. § 42.123(a), allowing Petitioner to submit Exhibits 1027–10318 as supplemental

<sup>-</sup>

<sup>&</sup>lt;sup>8</sup> Exhibit 1027 is the Declaration of Gordon MacPherson; Exhibit 1028 is the Declaration of Eileen D. McCarrier; Exhibit 1029 is the Declaration of Austin M. Schnell; Exhibit 1030 is the Supplemental Declaration of Rajesh K. Gupta, Ph.D.; and Exhibit 1031 is the Supplemental Declaration of Jacob Robert Munford.

IPR2020-01449 Patent 7,149,867 B2

information, which Petitioner contends confirms the public accessibility of Zhang, Gupta, and Chien references. Paper 27.

# b) Petitioner's Contentions

Petitioner contends Zhang was publicly accessible shortly after November 18, 1997, and no later than August 1, 2002, and, therefore, qualifies as prior art under 35 U.S.C. §§ 102(a) and 102(b). Pet. 17. Specifically, Petitioner argues (1) Zhang was published in 1997 by IEEE; (2) Zhang was distributed to conference attendees prior to or during the conference; (3) Zhang has been available on the IEEE Xplore website since at least as early as August 6, 2002; and (4) Zhang was catalogued by several university libraries by as early as November 18, 1997 and no later than August 1, 2002. *See* Pet. 17; Ex. 1010 ¶¶ 21–23; Ex. 1012 ¶¶ 15–20; Reply 4–8; Ex. 1030 ¶¶ 7–8; Ex. 1027 ¶ 11; Ex. 1031 ¶¶ 21–35.

Petitioner contends Gupta was publicly accessible by shortly after May 15, 2000, and therefore qualifies as prior art under 35 U.S.C. §§ 102(a) and 102(b). Pet. 19. Specifically, Petitioner argues (1) Gupta was published in 2000 by IEEE; (2) Gupta was distributed to conference attendees prior to or during the conference; (3) Gupta has been available on the IEEE Xplore website since at least as early as August 6, 2002; and (4) Gupta was catalogued by several university libraries as of May 15, 2000. *See* Pet. 19; Ex. 1010 ¶¶ 24–26; Ex. 1012 ¶¶ 21–26.

Petitioner contends Chien was publicly accessible by shortly after November 18, 1996, and therefore qualifies as prior art under 35 U.S.C. §§ 102(a) and 102(b). Pet. 21. Specifically, Petitioner argues (1) Chien was published in 1996 by IEEE; (2) Chien was distributed to conference attendees prior to or during the conference; (3) Chien has been available on the IEEE Xplore website since at least as early as August 6, 2002; and (4)

Chien was catalogued by several university libraries by shortly after November 18, 1996. *See* Pet. 19; Ex. 1010 ¶¶ 18–20; Ex. 1012 ¶¶ 27–32.

In support of its contentions that Zhang, Gupta, and Chien are printed publications, Petitioner relies on (1) the Declarations of Rajesh K. Gupta, Ph.D., who is one of the authors of Zhang, Gupta, and Chien; (2) the Declarations of Jacob Robert Munford, who has a Master of Library and Information Science degree and over ten years of experience in the library/information science field; (3) the Declaration of Gordon MacPherson, the Director of Board governance & IP Operations at IEEE; (4) the Declaration of Eileen D. McCarrier, Manager of Research Services at Pillsbury Winthrop Shaw Pittman LLP (Patent Owner's counsel); and (5) the Declaration of Austin M. Schnell, an associate at Pillsbury Winthrop Shaw Pittman LLP. Ex. 1010 ¶ 21; Ex. 1030; Ex. 1012 ¶ 2; Ex. 1031; Ex. 1027 ¶ 1; Ex. 1028 ¶ 1; Ex. 1029 ¶ 1.

Dr. Gupta testifies that (1) he presented each of Zhang, Gupta, and Chien at a conference sponsored or organized by IEEE in 1996, 1997, and 2000, respectively; (2) that based on his "experience in attending conferences [sponsored/organized] by the IEEE, and based on the general practice in the scientific and engineering community," he "believe[s] [each of Zhang, Gupta, and Chien] was distributed to the conference attendees prior to or during the conference"; (3) that each of Zhang, Gupta, and Chien "was subsequently published . . . by the IEEE"; 9 (4) and he "understand[s]

with Petitioner that this appeared to be a typographical error. Dec. n.7. Dr. Gupta corrected the error in his Supplemental Declaration. Ex. 1030 n. 1.

$<sup>^9</sup>$  In his original Declaration, Dr. Gupta states that Gupta was published in 1997. Ex. 1010 ¶¶ 25, 26. Patent Owner points out that Gupta was not authored until 2000. PO Resp. 23. In the Institution Decision, we agreed

that [each of Zhang, Gupta, and Chien] has been available from the IEEE Xplore website . . . since at least as early as August 6, 2002." Ex. 1010 ¶¶ 18–26. Dr. Gupta provides additional testimony that, based on his personal knowledge, each of the three references was distributed by the last day of its respective conference. Ex. 1030 ¶¶ 4–5, 7–8, 10–11.

Mr. Munford testifies that "[i]n preparing a material for public availability, a library catalog record describing that material would be created," which is typically written in Machine Readable Catalog ("MARC") code. Ex. 1012 ¶ 12. According to Mr. Munford, "the 008 field of the MARC record is reserved for denoting the date of creation of the library record itself" and "it is my experience that an item's MARC record indicates the date of an item's public availability." *Id.* He testifies that "[i]n my experience, the vast majority of library books cataloged and prepared for public availability in this fashion are made publicly available within 1 to 10 weeks of initial record creation." *Id.* ¶ 13. In addition, he testifies "[w]hen a material is held by multiple libraries, comparing the 008 fields of those records provides a specific window for public availability." *Id.*

For Zhang, Mr. Munford provides the MARC records that he secured from the online catalogs of the University of Cincinnati, Cornell University, and Michigan State University, purporting to show catalog dates of November 18, 1997, August 1, 2002, and November 18, 1997, respectively. *Id.* ¶¶ 16–19. Based on these records, Mr. Munford opines that Zhang "was made available and accessible to the public by shortly after November 18, 1997 and certainly no later than August 1, 2002." *Id.* ¶20.

For Gupta, Mr. Munford provides the MARC records that he secured from the online catalogs of Georgia Tech, Notre Dame University, and Linda Hall Library, purporting to show catalog dates of May 15, 2000 for all

three libraries. *Id.* ¶¶ 22–25. Based on these records, Mr. Munford opines that Gupta "was made available and accessible to the public by shortly after May 15, 2000." *Id.*  $\P$  26.

For Chien, Mr. Munford provides the MARC records that he secured from the online catalogs of Cornell University, the University of Dayton, and Indiana University, purporting to show catalog dates of November 22, 1996, November 18, 1996, and November 18, 1996, respectively. *Id.* ¶¶28–31. Based on these records, Mr. Munford opines that Chien "was made available and accessible to the public by shortly after November 18, 1996." *Id.* ¶ 32.

Mr. Munford also provides additional testimony that he personally retrieved, or directed others at Pillsbury Winthrop Shaw Pittman LLP to retrieve, copies of the three references from various libraries for review, and that he personally reviewed those copies. Ex. 1031 ¶¶ 19–69. Mr. Munford testifies that at the time of his original Declaration, all libraries within his usual travel range had been closed, and the area where he lived was under a travel advisory due to the COVID-19 pandemic. *Id.* ¶ 17.

Mr. MacPherson testifies that (1) according to IEEE's standard practices, copies of proceedings were made available no later than the last day of the conference; (2) each of the three references are currently available for download from the IEEE digital library, IEEE Xplore; and (3) IEEE Xplore populates the information such as the date of publication and additional publication information, using the metadata associated with the publication. Ex. 1027 ¶¶ 1, 11–13.

Ms. McCarrier testifies that that she personally received a pdf copy of Zhang from the Library of the Missouri University of Science and

Technology, Rolla, Missouri, part of the University of Missouri system, and a pdf copy of Gupta from the Georgia Tech Library. Ex. 1028 ¶¶ 1, 6–9.

Mr. Schnell testifies that that he personally retrieved a physical copy of Gupta and Chien from the University of Texas library. Ex.  $1029 \, \P \, 1-3$ .

# c) Patent Owner's Contentions

In its Response, Patent Owner disputes the prior art status of Zhang, Gupta, and Chien. PO Resp. 19–29. Specifically, Patent Owner contends that Petitioner has not established that Zhang, Gupta, and Chen are printed publications because Petitioner has not shown that they were publicly accessible. *Id.* Patent Owner presents the identical argument that it presented in the Preliminary Response. *See* Paper 9, 26–35. Patent Owner does not address the printed publication issue in the Sur-reply. *See generally* Sur-reply.

First, Patent Owner argues that Dr. Gupta does not provide firsthand knowledge as to whether the references were actually distributed to attendees, and Petitioner has provided no evidence that the references were ever circulated at the conferences. PO Resp. 22–23.

Second, Patent Owner argues that Petitioner "provides no indication of how the IEEE Xplore website operated [in 2002, when the references were purportedly uploaded], how information was organized on the website, nor any evidence of the steps a user would have needed to take to find the *Zhang* or *Gupta* references once uploaded." PO Resp. 24. Patent Owner also asserts that "even today, a reasonable search of the website using key concepts from the '867 patent does not identify the asserted references." *Id.* Therefore, according to Patent Owner, Petitioner has not shown that the references were "meaningfully indexed such that an interested artisan exercising reasonable due diligence would have found" the references on the

IEEE Xplore website. *Id.* (citing *Acceleration Bay, LLC v. Activision Blizzard, Inc.*, 908 F.3d 765, 774 (Fed. Cir. 2018); *Samsung Elec. Co. v. Infobridge Pte. Ltd.*, 929 F.3d 1363, 1369 (Fed. Cir. 2019)).

Third, Patent Owner argues that Mr. Munford's testimony is insufficient to show that the references were publicly accessible for two reasons. PO Resp. 27–28. First, Patent Owner argues that the records Mr. Munford relies upon are insufficient because, with the exception of the Chien reference, the records only refer to the name or general subject matter of the conference, as opposed to the name of the author or title of the reference. *Id.* Therefore, according to Patent Owner, there is no way to determine the content or precise subjects covered using reasonable diligence. *Id.* Second, Patent Owner argues that Mr. Munford only shows when the references were catalogued, but the references would not be available until they are shelved and available for distribution. *Id.* at 28. According to Patent Owner, it is not reasonable to presume that the references must have been available shortly after cataloguing. *Id.*

# d) Analysis

The determination of whether a document is a "printed publication" under 35 U.S.C. § 102 "involves a case-by-case inquiry into the facts and circumstances surrounding the reference's disclosure to members of the public." *In re Klopfenstein*, 380 F.3d 1345, 1350 (Fed. Cir. 2004). "Because there are many ways in which a reference may be disseminated to the interested public, 'public accessibility' has been called the touchstone in determining whether a reference constitutes a 'printed publication." *Jazz Pharm., Inc. v. Amneal Pharm., LLC*, 895 F.3d 1347, 1355 (Fed. Cir. 2018) (quoting *In re Hall*, 781 F.2d 897, 898–99 (Fed. Cir. 1986)).

"Whether a reference qualifies as a printed publication under § 102 is a legal conclusion based on underlying fact findings." *Acceleration Bay*, 908 F.3d at 772. "A reference is considered publicly accessible if it was 'disseminated or otherwise made available to the extent that persons interested and ordinarily skilled in the subject matter or art, exercising reasonable diligence, can locate it." *Id.* (citing *Jazz*, 895 F.3d at 1355–1356). "If accessibility is proved, there is no requirement to show that particular members of the public actually received the information." *Constant v. Advanced Micro-Devices, Inc.*, 848 F.2d 1560, 1569 (Fed. Cir. 1988).

After considering the arguments and weighing the evidence presented by the parties, we determine that Petitioner has shown by a preponderance of the evidence that Zhang, Gupta, and Chien were publicly accessible before the priority date, and, therefore qualify as prior art under 35 U.S.C. § 102(b).

Zhang, on its face, is a paper from the *Proceedings of the International Conference on Computer Design, VLSI in Computers and Processors*, which took place on October 12–15, 1997, in Austin, Texas, and was sponsored by the IEEE Computer Society Technical Committee on Design Automation, IEEE Circuits and Systems Society. Ex. 1003, 1. The copyright page indicates a copyright date of 1997 by IEEE, ISBN numbers, IEEE order plan catalog numbers, and addresses in California and New Jersey where additional copies may be ordered. *Id.* at 2. The Table of Contents for the Proceedings indicates over 700 pages of papers associated with various sessions, where Zhang is at pages 150–156. *Id.* at 3–18. At the bottom of the first page of the Zhang paper, it states "1063-6404/97 \$10.00 © 1997 IEEE." *Id.* at 12.

Gupta, on its face, is a paper from the *Proceedings of the IEEE Computer Society Workshop on VLSI 2000, System Design for a System-on-Chip Era*, which took place on April 27–28, 2000, in Orlando, Florida, and was sponsored by the IEEE Computer Society Technical Committee on VLSI. Ex. 1004, 3. The copyright page indicates a copyright date of 2000 by IEEE, ISBN numbers, IEEE order plan catalog numbers, and addresses in California and New Jersey where additional copies may be ordered. *Id.* at 4. The Table of Contents for the Proceedings indicates over 150 pages of papers associated with various sessions, where Gupta is at pages 75–80. *Id.* at 5–12. At the bottom of the first page of the Gupta paper, it states "0-7695-0534-1/00 \$10.00 © 2000 IEEE." *Id.* at 8.

Chien, on its face, is a paper from the *Proceedings of the Frontiers* '96, The Sixth Symposium on the Frontiers of Massively Parallel Computing, which took place on October 27–31, 1996, in Annapolis, Maryland, and was sponsored by the IEEE Computer Society. Ex. 1005, 1. The copyright page indicates a copyright date of 1996 by IEEE, ISBN numbers, IEEE order plan catalog numbers, and addresses in California and New Jersey where additional copies may be ordered. *Id.* at 2. The Table of Contents for the Proceedings indicates over 350 pages of papers associated with various sessions, where Chien is at pages 336–345. *Id.* at 3–16. At the bottom of the first page of the Chien paper, it states "1088-4955/96 \$5.00 © 1996 IEEE." *Id.* at 7.

Although not dispositive, there is relevant evidence that supports our finding that each of Zhang, Gupta, and Chien were publicly accessibility prior to the critical date. Specifically, as set forth above, each bear multiple conventional indicia of publication and such as a copyright date, ISBN number and IEEE order plan catalog number, price, indicia of publication by

an established publisher, IEEE, and instructions for ordering additional copies, all of which are relevant evidence supporting a finding of public accessibility. *See Nobel Biocare Services AG v. Instradent USA, Inc.*, 903 F.3d 1365, 1378 (Fed. Cir. 2018) ("[a]lthough the ABT Catalog's date is not dispositive of the date of public accessibility, its date is relevant evidence"); *see also VidStream LLC v. Twitter, Inc.*, 981 F.3d 1060, 1065 (Fed. Cir. 2020) ("When there is an established publisher there is a presumption of public accessibility as of the publication date.").

In our Institution Decision, we agreed with Patent Owner that Dr. Gupta's testimony as to whether the papers were distributed to participants at the conference was speculative, because he had not provided firsthand knowledge of whether that had actually happened. Dec. 41. In his original Declaration, Dr. Gupta testifies that he "believe[s]" that the papers were distributed to the conference attendees prior to or during the relevant conference, yet in his Supplemental Declaration, Dr. Gupta testifies that he "confirm[s] based on my personal knowledge that [the] paper[s]... [were] included in the IEEE printed publication that was distributed to the conference attendees during the conference." Ex. 1010 ¶¶ 18, 19, 21, 22, 24, 25; Ex.  $1030 \, \P$  5, 8, 11. At his deposition, he testified that his testimony changed because "it was a recollection at that time," but later had become certain. Ex. 1039, 11:7–13. We credit Dr. Gupta's deposition testimony which is corroborated based upon Mr. MacPherson's testimony that "[i]n accordance with IEEE's standard practices, copies of the proceedings were made available no later than the last day of the conference." See Ex. 1010 ¶¶ 18, 21, 24; Ex. 1030¶ 3, 5, 8, 11; Ex. 1027¶¶ 11–13. We also find that Dr. Gupta's refreshed memory is supported by his experience in attending conferences sponsored by IEEE. Ex. 1030 ¶ 2. This testimony by Dr. Gupta and Mr. MacPherson, supporting that the three papers were distributed to participants at the conference, is unrebutted.

We also determine that the MARC records from the various libraries provided by Mr. Munford for Zhang, Gupta, and Chien, and the accompanying testimony by Mr. Munford, including his knowledge as to standard library practices relating to MARC records (e.g., Ex. 1012 ¶¶ 12, 13; Ex. 1031 ¶¶ 13–14), is sufficient evidence to show that Zhang, Gupta, and Chien were cataloged and publicly accessible. See Ex. 1012 ¶¶ 12–32; Ex. 1031 ¶¶ 19–69. Mr. Munford provides extensive, unrebutted testimony pertaining to the authenticity of the papers reviewed that were retrieved from the libraries, as well as the MARC records associated with those papers. *Id.* We credit Mr. Munford's testimony that Zhang, Gupta, and Chien, in their entirety, were properly catalogued and publicly available. *Id.* For example, Mr. Munford testifies that all four MARC records for the four copies of Zhang that were retrieved from four different libraries accurately describe its title, publisher, and ISBN, match the number of pages in the various copies he retrieved, and contain "008" fields that "designate the date of record creation" with an entry of "November 18, 1997" or "August 1, 2002." See Ex. 1031 ¶¶ 33–34. In addition, Mr. Munford testifies that the copy of Zhang that was retrieved from the University of Missouri library by Ms. McCarrier has a handwritten date of "11-25-97" on the top of the first table of contents page, one week after the date on the MARC record. *Id.* ¶35. Mr. Munford provides similar testimony for the Gupta and Chien papers. *Id.* ¶¶ 36-69.

Patent Owner does not dispute that Zhang, Gupta, and Chien were available on the IEEE website as of August 6, 2002. *See* PO Resp. 25 ("All Petitioner has shown, is that the references purportedly were placed on a

website in 2002 . . . . "). Rather, Patent Owner argues that Petitioner has not shown that the references were "meaningfully indexed in a way that they might be located using reasonable diligence." *Id.* at 21; *see also id.* at 31. However, "indexing is not 'a necessary condition for a reference to be publicly accessible'; it is but one among factors that may bear on public accessibility." *Voter Verified, Inc. v. Premier Election Solutions, Inc.*, 698 F.3d 1374, 1380 (Fed. Cir. 2012) (citing *In re Lister*, 583 F.3d 1307, 1312 (Fed. Cir. 2009)). Thus, "while often relevant to public accessibility, evidence of indexing is not an absolute prerequisite to establishing online references . . . as printed publications within the prior art." *Id.* Nonetheless, Mr. Munford provides unrebutted testimony and supporting evidence regarding the indexing provided on the IEEE website in the 2002 timeframe, which we credit. Ex. 1031 ¶¶ 15–16, 70–87.

Accordingly, we find that the totality of the evidence provided by Petitioner, including (1) the indicia of publication and public accessibility on the face of each of the references; (2) IEEE's standard practices to distribute papers of the proceedings no later than the last day of the conference; (3) the availability of the references on the IEEE website; and (4) the cataloguing of the Proceedings for each of the papers in various libraries, demonstrates by a preponderance of the evidence that each of Zhang, Gupta, and Chien were publicly accessible prior to the priority date of June 18, 2003.

# E. Ground 1: Obviousness Over Zhang and Gupta

Petitioner contends claims 1, 2, 4–8, and 13–19 would have been obvious over the combination of Zhang and Gupta, and relies on the Declaration of Dr. Stanley Shanfield, Ph.D. (Ex. 1006) in support of its contentions. Pet. 5, 28–87. After reviewing the entire record developed at trial, as explained below, we determine that Petitioner has shown, by a

preponderance of the evidence, that claims 1, 2, 4–8, and 13–19 are unpatentable over the combination of Zhang and Gupta.

Patent Owner's General Arguments as to Zhang and Gupta. Patent Owner makes two general arguments as to Zhang and Gupta. First, Patent Owner argues that Zhang and Gupta teach away from the claimed invention. See PO Resp. 16 ("Zhang explicitly mentions that the main application remains in software (executed on the CPU) and programmable logic is used only for hardware adaptations (that remain static for the duration of a specific application run), thus teaching away from the invention of the '867 patent."); 19 ("Like Zhang, in Gupta, the main application remains in software (executed on the CPU), and programmable logic is used only for hardware adaptations that remain static for the duration of a specific application run, thus teaching away from the invention of the '867 patent."); see also Sur-reply 1–2. In support of its argument, Patent Owner relies on the testimony of Dr. Mangione-Smith. PO Resp. 16, 19 (citing Ex. 2028 ¶ 70).

A reference teaches away from a claimed invention if it "criticize[s], discredit[s], or otherwise discourage[s]" modifying the reference to arrive at the claimed invention. *In re Fulton*, 391 F.3d 1195, 1201 (Fed. Cir. 2004). Neither Patent Owner nor Dr. Mangione-Smith identifies where Zhang and Gupta criticize, discredit, or otherwise discourage the claimed invention. Rather, Patent Owner and Dr. Mangione-Smith argue that the references *do not teach* the disclosure in the '867 patent. For example, Dr. Mangione-Smith provides testimony that Zhang does not "instantiate an algorithm as hardware." Ex. 2028 ¶ 68, 70 ("[t]he main application algorithm . . . are not instantiated as hardware"; "the algorithms that comprise the application discussed in *Zhang* also 'remain in software'"). This is not sufficient to

show that the references teach away from the claimed invention. *See Galderma Labs.*, *L.P. v. Tolmar*, *Inc.*, 737 F.3d 731, 738 (Fed. Cir. 2013) ("A reference does not teach away, . . . if it merely expresses a general preference for an alternative invention but does not criticize, discredit, or otherwise discourage investigation into the invention claimed."). We, therefore, find this argument unavailing.

Second, Patent Owner argues that Zhang is not an enabling prior art reference. *See* PO Resp. 15. However, "[u]nder § 103, . . . a reference need not be enabled; it qualifies as a prior art, regardless, for whatever is disclosed therein." *Amgen Inc. v. Hoechst Marion Roussel, Inc.*, 314 F.3d 1313, 1357 (Fed. Cir. 2003) (citing *Symbol Techs., Inc. v. Opticon, Inc.*, 935 F.2d 1569, 1578 (Fed. Cir. 1991) ("enablement of the prior art is not a requirement to prove invalidity under § 103")); *Reading & Bates Constr. Co. v. Baker Energy*, 748 F.2d 645, 652 (Fed. Cir. 1984). We, therefore, also find this argument is unavailing.

## 2. Analysis of Independent Claim 1

- a) Limitation of the preamble: "A reconfigurable processor that instantiates an algorithm as hardware comprising"

- (1) The Parties' Contentions

The parties agree that the preamble limits claim 1. *See* Pet. 28–30; PO Resp. 30, 33. Petitioner asserts that Zhang discloses the preamble. Pet. 28–30. For example, Petitioner relies on Zhang's architecture "that integrates small blocks of programmable logic into key elements of a baseline architecture, including processing elements, components of the memory hierarchy, and the scalable interconnect, to provide *architectural adaptation* – the customization of architectural mechanisms and policies to

match an application." *Id.* at 28 (citing Ex. 1003, 13) (bolding omitted). Petitioner asserts that Zhang's Figure 2 illustrates "a reconfigurable processor that includes a CPU, cache memory, and processor main memory, each integrated with blocks of programmable logic over a flexible interconnect." *Id.* at 28–29 (citing Ex. 1003, 12–15, Figs. 2 and 4). Petitioner contends, with supporting testimony from Dr. Shanfield, that a person of ordinary skill in the art "would understand Zhang's processor architecture, which integrates 'blocks of programmable logic into key elements' customized to 'match an application,' to disclose a computing device that contains reconfigurable components that can, through reconfiguration, instantiate an application's algorithm(s) as hardware." *Id.* at 30 (citing Ex. 1006 ¶ 131).

Patent Owner argues that (1) Zhang's processor is a conventional CPU, not a reconfigurable processor; and (2) Zhang's processor does not "instantiate an algorithm as hardware." PO Resp. 33–37; Sur-Reply 2–5.

According to Patent Owner, Zhang "uses programmable logic (FPGA) as means to deliver data for use by [a] conventional CPU." PO Resp. 34. Patent Owner contends that Figure 2 of Zhang shows the use of a CPU and small pockets of reprogrammable logic blocks, not a reconfigurable processor. *Id.* Patent Owner's annotated Figure 2 is reproduced below:

Figure 2. An Architecture for Adaptation

Figure 2 of Zhang, above, depicts an architecture for adaptation, with boxes depicting a CPU, Network Interface, Memory, and Cache, each with corresponding "Programmable Logic." Patent Owner annotates Figure 2, drawing a red line around the CPU, and green lines around the "Programmable Logic." Patent Owner contends that this "clearly shows the use of a CPU (indicated in red) that executes all algorithms that comprise the application that remain in [sic] software, and only small pockets of reprogrammable logic blocks (indicated in green)." PO Resp. 35.

Patent Owner argues that Zhang's "programmable logic is only implemented in small blocks for specific intermediate purposes, such as the interface between CPU and cache, the network interface, or the memory interface." *Id.* at 36 (citing Ex. 1003, Fig. 2). For this reason, Patent Owner contends that Zhang's architecture is "incapable of 'instantiating an

algorithm as hardware." Id. (citing Ex.  $2028 \, \P \, 42$ ). Patent Owner further argues that "the CPU hardware is static and cannot be adapted to a specific application . . . [and] [t]his is why Zhang teaches that its entire application must remain in software." Id. Patent Owner relies on Dr. Mangione-Smith's testimony in support of its arguments that Zhang does not "instantiate an algorithm as hardware." E.g., id. at 35 (citing Ex.  $2028 \, \P \, 70$ ).

Patent Owner also argues that Zhang "fails to disclose any capability to reconfigure its small reprogrammable logic blocks on a per application basis." *Id.* at 37 (citing Ex. 2028 ¶ 68). Patent Owner argues that, at most, Zhang's architecture could "create application specific hardware instantiations for the cache, network, and memory interfaces," but "the CPU hardware is static and cannot be adapted to a specific application." *Id.* at 36. Patent Owner also argues that Zhang "discloses only relatively minor hardware architectural adaptations . . . [which] is quite different from the physical adaptation of the entire reconfigurable processor to the specific needs of a particular application taught in the '867 patent." *Id.* at 36–37 (citing Ex. 1003, 15–16; Ex. 2028 ¶ 66–67). Patent Owner contends that "these relatively minor hardware adaptations are not application specific, but application class specific." *Id.* at 37 (citing Ex. 2028 ¶ 42).

In Reply, Petitioner argues that Patent Owner introduces requirements that are not commensurate with the scope of the claim or the agreed construction of a "reconfigurable processor." Reply 10. Petitioner further argues that Patent Owner's arguments conflict with the disclosure in the '867 patent and the prosecution history. *Id.* at 11.

Petitioner also argues that Patent Owner mischaracterizes Zhang as "disclosing a 'static' 'conventional' CPU incapable of instantiating an algorithm as hardware." *Id.* at 12. According to Petitioner, Patent Owner's

annotated Figure 2 is incorrect, and Patent Owner is "wrong to focus its analysis only on Zhang's CPU-labeled block alone rather than the reconfigurable processor that Petitioner and Dr. Shanfield identified." *Id.* Petitioner's annotated Figure 2 of Zhang is reproduced below.

Figure 2. An Architecture for Adaptation

Figure 2 of Zhang, above, depicts an architecture for adaptation, with boxes depicting a CPU, Network Interface, Memory, and Cache, each with corresponding "Programmable Logic." Petitioner annotates Figure 2 with a pink box around the entirety of the CPU, Network Interface, Memory, and Cache boxes. Reply 12. Petitioner further argues that "Zhang expressly discloses integrating programmable logic *into the processing elements*, which Zhang identifies *separately* from the memory hierarchy, scalable interconnect, and network interface." *Id.* at 13 (citing Ex. 1003, 13; Fig. 2). According to Petitioner, "Zhang's processing elements—whether labeled 'processor' or 'CPU'—are indeed reconfigurable." *Id.*

Additionally, Petitioner argues that Zhang's reconfigurable processor can instantiate an algorithm as hardware, because it teaches "optimizing matrix multiplication computations using the customization provided by its programmable logic to improve computational processing." *Id.* at 14 (citing Ex. 1003, 12). Petitioner contends that "[n]othing about [Zhang's] statement [that the 'application remains in software'] precludes compiling one (or more) of an application's algorithms and instantiating it as hardware." *Id.* According to Petitioner, this is consistent with the teachings in the '867 patent. *Id.* Petitioner further contends that Zhang is "merely distinguish[ing] its approach from conventional co-processing architectures that must repartition hardware and software functionality and reimplement the co-processing hardware every time a new application is run." *Id.* at 15 (citing Ex. 1003, 12).

In the Sur-reply, Patent Owner contends that "[t]here is a stark difference between including some reconfigurable components in a conventional CPU as compared to using reconfigurable hardware to actually 'instantiate an algorithm as hardware' as claimed." Sur-reply 2–3. Patent Owner argues that in Zhang, "the processor running the main application is a conventional CPU, not a reconfigurable processor." *Id.* at 3. In support, Patent Owner again refers to Figure 2 of Zhang, and argues that "the reconfigurable logic is only used at the periphery of the conventional CPU." *Id.* According to Patent Owner, Figure 2 "leaves no doubts that the programmable logic is *next to* – not *contained in* – the CPU." *Id.* at 4. Patent Owner contends that the "programmable logic is only implemented in small blocks for specific intermediate purposes between components, such as the interface between CPU and cache, the network interface, or the memory interface." *Id.* Patent Owner further contends, with supporting

IPR2020-01449 Patent 7,149,867 B2

testimony from Dr. Mangione-Smith That Zhang's architecture is incapable of 'instantiating an algorithm as hardware.'" *Id.* (citing Ex. 2028 ¶ 42).

### (2) Analysis

As discussed above, the parties agree, and we determine, that a "reconfigurable processor" is construed as "a computing device that contains reconfigurable components such as FPGAs and can, through reconfiguration, instantiate an algorithm as hardware." See Ex. 1001, 5:26-29. For the reasons advanced by Petitioner and as discussed below, we agree with Petitioner and find that Zhang teaches the claimed "reconfigurable processor." See Pet. 28–30; Reply 11–15. Patent Owner's arguments are premised on Zhang teaching a conventional, static processor and not a reconfigurable processor. In presenting these arguments, Patent Owner focuses on Zhang's CPU in Figure 2. PO Resp. 35–36; Sur-Reply 3– 4. But Petitioner relies not only on the CPU to teach the "reconfigurable processor," but on the entire architecture depicted in Figure 2, which "includes a CPU, cache memory, and processor main memory, each integrated with blocks of programmable logic over a flexible interconnect." Pet. 29. This is consistent with the construction of the "reconfigurable processor." Patent Owner's arguments do not squarely address Petitioner's contentions, or explain why Zhang does not teach the "reconfigurable processor," as construed by the parties and which we have adopted.

Patent Owner's focus on the CPU of Figure 2 – and attempt to separate it from the rest of the components – carries through its arguments. For example, Patent Owner admits that Zhang's architecture can "create application specific hardware instantiations for the cache, network, and memory interfaces," but attempts to distinguish Zhang's CPU as "static and cannot be adapted to a specific application . . . [which] is why *Zhang* teaches

that its entire application must remain in software." PO Resp. 36; *see also* Ex. 2028 ¶ 68. But Zhang's disclosure does not support such a distinction.

Zhang states "We propose an architecture that *integrates small blocks*" of program mable logic into key elements of a baseline architecture, including processing elements, components of the memory hierarchy, and the scalable interconnect, to provide architectural adaptation – the customization of architectural mechanism and policies to match an application." Ex. 1003, 13 (first and third emphases added). That is, Zhang states that the small blocks of programmable logic are integrated into key elements of a baseline architecture, including processing elements and components of the memory hierarchy, and this is depicted in Figure 2. Ex. 1003, 13; Fig. 2 (showing programmable logic integrated with a CPU, cache, memory, and network interface). Given this disclosure in Zhang, along with the inclusion of "programmable logic" in the "CPU," we do not agree that Zhang's CPU is "static and cannot be adapted to a specific application." See PO Resp. 36. Nor, for the same reasons, do we agree that Zhang's programmable logic is not "contained in" the CPU (or the memory), but is "next to" it, as Patent Owner argues. See Sur-reply 4. As Petitioner persuasively argues, Patent Owner's arguments regarding Zhang are not commensurate with the parties' agreed construction of the term "reconfigurable processor" or the claim language. See Reply 10–11.

Patent Owner contends that Zhang's statement that "the entire application remains in software" evidences that Zhang's architecture does not instantiate an algorithm as hardware. *See* PO Resp. 34–37; Ex. 2028 ¶ 67. Zhang states: "In addition, because the entire application remains in software while the underlying hardware is adapted for system performance,

our approach improves over co-processing architectures by preserving machine usability through software." *See* Ex. 1003, 14.

Dr. Mangione-Smith testifies that a person of ordinary skill in the art "would understand [Zhang's] disclosure to indicate that system performance is adapted *transparently* to the application and its algorithms, *i.e.*, that these adaptations do not teach that any part of the application actually run[s] in *Zhang*, that is any of the algorithms that actually make up the application that remains in software, are instead instantiated in hardware." Ex. 2028 ¶ 70 (emphasis in original). He states that "this fact is confirmed by the last part of the same cited sentence, [which states] our approach improves over co-processing architectures *by preserving machine usability through software*." *Id.* According to Dr. Mangione-Smith, "[m]achine useability through software aims to retain the flexibility of implementing software on general purpose hardware such as the conventional CPU used by *Zhang*."

Patent Owner's argument as to the instantiation relies on a finding that Zhang's CPU is a static, conventional processor. *See* PO Resp. 36 ("This architecture is incapable of 'instantiating an algorithm as hardware" (citing Ex. 2028 ¶ 42); "[T]he CPU hardware is static and cannot be adapted to a specific application . . . [t]his is why *Zhang* teaches that its entire application must remain in software."). As stated above, we reject that argument. Moreover, Patent Owner admits that Zhang's architecture could "*create application specific hardware instantiations* for the cache, network, and memory interfaces." PO Resp. 36 (emphasis added).

We do not find Dr. Mangione-Smith's testimony availing, given the disclosure in Zhang. Specifically, we do not agree that Zhang's statement that "our approach improves over co-processing architectures by preserving

machine usability through software" supports that the architecture does not instantiate an algorithm as hardware. Rather, we find persuasive Petitioner's contention that in that statement Zhang is simply distinguishing itself from conventional co-processing architectures. *See* Reply 15. We do not agree that this disclosure in Zhang precludes "instantiating an algorithm as hardware," given that Zhang extensively refers to "customizing architectural mechanisms and policies to match an application," "application-specific hardware assists," "application-specific optimizations," "architectural customization," "architectural adaptation," and "the underlying hardware is adapted." *E.g.*, Ex. 1003, 12–14.

Patent Owner draws a distinction between hardware applications that are application specific and hardware applications that are application class specific, arguing that Zhang teaches the latter and, therefore, does not "disclose any capability to reconfigure its small reprogrammable logic blocks on a per application basis." PO Resp. 37. Patent Owner's argument is not supported by Zhang's disclosure. See, e.g., Ex. 1003, 12 ("the goal of customizing architectural mechanisms and policies to match an application" and "application-specific hardware assists and policies can provide substantial improvements in performance on a per application basis"); 13 ("the customization of architectural mechanisms and policies to match an application"), 14 ("[a]rchitectural adaptation provides the mechanisms for application-specific hardware assists") (emphasis added).

In summary, we agree with Petitioner, and find credible Dr. Shanfield's testimony that a person of ordinary skill in the art "would understand Zhang's processor architecture that integrates 'programmable logic' customized to 'match an application' to disclose a computing device that, through reconfiguration, instantiates an algorithm as hardware. *See* Ex.

IPR2020-01449 Patent 7,149,867 B2

1006¶ 131. Moreover, as Dr. Shanfield points out, the architecture's name is "MORPH" - (MultiprocessOr) with Reconfigurable Parallel Hardware. *Id.*; *see* Ex. 1003, 14.

After considering the evidence and arguments of the complete record, we determine that Petitioner has shown, by a preponderance of the evidence, that Zhang teaches the preamble.

b) Limitation 1(a): "a first memory having a first characteristic memory bandwidth and/or memory utilization"

Petitioner asserts that Zhang discloses this limitation. Pet. 30–31. Specifically, Petitioner relies on Zhang's L1 cache, contending that the L1 cache is a first memory with a first characteristic memory bandwidth because "L1 cache has a transfer rate (memory bandwidth) of 16B/5 cycles." *Id.* (citing Ex. 1003, 15 Table 1, Fig. 4). Petitioner also relies on Zhang's Figure 5, contending the "Cache" shown in Figure 5 also teaches a first memory. *Id.* at 52 (citing Ex. 1003, Fig. 5).

Patent Owner does not specifically respond to these arguments. *See generally* PO Resp.

After considering the evidence and arguments of the complete record, we determine that Petitioner has shown, by a preponderance of the evidence, that Zhang teaches limitation 1(a).

c) Limitation 1(b): "a data prefetch unit coupled to the first memory"

Petitioner contends that Zhang in combination with Gupta discloses a data prefetch unit as recited in limitation 1(b). Pet. 32–36. Petitioner relies on Zhang's data prefetcher that is coupled to LI cache and L2 cache. *Id.* at 32–33 (citing Ex. 1003, 15, Fig. 4; Ex. 1006¶ 138). With supporting testimony from Dr. Shanfield, Petitioner asserts that "Zhang teaches a data

prefetcher that (i) is implemented in reconfigurable (programmable) logic; (ii) is a set of logic that performs a specific operation; (iii) is coupled to the first memory (L1 cache); and (iv) moves data between a first memory (L1 cache) and a second memory (L2 cache or main memory), which together are a collection of memories constituting a 'memory hierarchy.'" *Id.* at 34 (citing Ex. 1006 ¶ 138).